Parallel Input Serial Output Shift Register Verilog Code

Verilog code for serial Adder Block Diagram: `resetall `timescale 1ns/1ns //shift register to store the two inputs a and b to be added module shift(y,d,clk); input [3:0] d. Nov 3, 2015 - module sr_74LV165A ( input DS, CP, CE_n, PL_n, input D0, D1, D2, D3, D4, D5, D6, D7, output Q7, Q7_n ); reg [0:7] shr; wire clk; assign clk.

Shift Register using verilog |

We will now consider a shift register. Our shift register has an s_in input entering on its left hand side. At each clock cycle, the content of the register shifts to the right and s_in enters into the leftmost bit or the MSB bit. The whole design also has and output that we are c calling s_out. At each clock cyccle the right most bit of the register comes out.

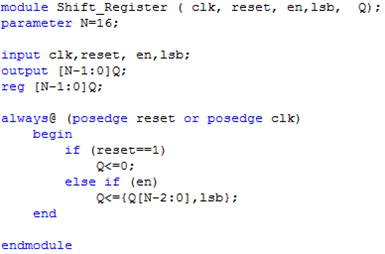

The picture shows the scheme of the shift register.

Here is the verilog implemmentation of shift register.

Explanation |

Initially the reg value of undefined and hence we have placed 4'bxxxx in its value.

Because of the assign statement

the initial value of s_reg[0] is also 0.

When the reset pulse is applied the r_reg becomes 0000 at the next rising edge of clock. Note that the period of the negative level of the reset sould last at least to the next rising edge of the clock

At this stage, the value of s_out also becomes 0 ( right after the rising edge of the clock).

Now the s_in value is supplied sometimes before the next rising edge of the clock. Now because of the assign statement

the wire r_next is driven by the value of s_in and [3:1] bits of r_reg.

And so, after the application of the s_in, at the next rising edge of the clock, the statement

in the always loop takes effect. which essentially results in updating the r_reg value with its value shifted to right and s_in coming in at its MSB.

The testbech for the Serial shift register

Exercizes

1. In test bench the shift register is instantiated with N=2. Verify that it behaves as expected. Repead the testbench and verification for N=4

2. Write the above code for left shift in place of right shift. The data now comes out of the MSB. The data enters from LSB.

Introduction

Parallel Input Serial Output Shift Register Verilog Code

The shift registers store a value and shifts it. They are extremely useful. They are used to convert information from parallel to serial (and vice versa) for use in syncronous communications. Communications through SPI, I2C, and more are implemented with these registers. The also allow us to perform the operations of multiplying by powers of 2 and dividing by powers of 2 for integers.

In this chapter we will use them to generate a sequence of 4 states on the LEDs of the iCEstick, moving the lights clockwise.

Description of the register.

The shift register we will use is as follows:

The output of the register is N bits (in our example we will use a 4 bit register). It has an N-bit Parallel input, which allows us to load the register with a new value. The load_shift signal allows us to determine the operating mode: when it is at 0, a new value is loaded when a rising edge of the clock arrives. When it is at 1, a right shift is made on the rising edge of the clock.

In this shift the most significant bit is lost and the new value is read from the serin input (serial input). If we have the initial value 1'b1001 stored, and the signal load_shift is at 1, while serin is at 0 and a rising edge of the clock arrives, we get the value: 0010. On the next cycle (if serin statys 0) we get 0100, then 1000, and then 0000.

shift4: Rotation of bits

As an example we will use a 4-bit shift register to rotate a sequence of bits and display them by the 4 LEDs on the iCEstick. The sequence obtained by the LEDs will depend on the initial value loaded in the register.

The block diagram of the shift4 component is:

The main component is a 4-bit shift register. It's clock input is connected to the iCEstick clock via a prescaler component to lower it's frequency and to be able to see the shifting of the bits in the LEDs.

The most significant bit of the register (data[3]) is connected directly to the serin input, so that bit rotation is achieved (the most significant one becomes the least significant).

Via the parallel input we introduce the initial value, which by default will be 1'b0001. Rotation will show the sequence 0010, 0100, 1000, and 0001.

The initial load is done using an initializer, as shown in chapter 9. It is connected to the input load_shift, so that initially it is 0 and when the first clock edge arrives it changes to 1, loading the initial value and changing to shift mode. The rest of the cycles will be shifting. This is an example of how the initializer works.

Hardware Description

Shift Register

The shift register is described with very few lines. It is a process that depends on the rising edge of the clock.

In the load mode the initial value (INI) is output. In the shift, the three least significant bits are shifted left and serin is concatenated as the least significant bit. This is done with the concatenation operator{}: a fourth wire is added to the three wires defined by data[2:0].

Shift4 Component

The final component of shift4 has 2 parameters: the **number of bits of the prescaler (NP), which determines the speed of ration of the bits, and the initial value (INI) to be loaded, which determines the sequence. By default, this initial value is 4'b0001

The code to describe the complete shift4 component is:

Thie shift register has been directly implemented as a process in the component itself, rather than as a separate componente (hierarchical design).

Synthesis of the FPGA

To synthesize it in the fpga we will connect the data outpus to the LEDs and the clock input to that of the iCEstick.

Synthesize with the command:

The resources used are:

| Resource | utilization |

|---|---|

| PIOs | 4 / 96 |

| PLBs | 10 / 160 |

| BRAMs | 0 / 16 |

To load into the FPGA we execute:

In this Youtube video you can see the output of the LEDs:

Simulation

The testbench is a basic one, which instantiates the shift4 component, with 1 bit for the prescaler parameter (to make the simulation run over less clock cycles) and an initial value of 4'b0001 for the shift register. It has a process for the clock signal, and one for initialization of simulation.

The simulation is run with:

The result in gtkwave is:

We see how initially the register has an undefined value (x) and when the first rising edge arrives it is initialized with the value 0001, thanks to the initializer circuit). In the following cycles we see how the bit is shifted to the left: 0010, 0100, 1000 and finally returns to the initial value: 0001, repeating the sequence until the end of simulation.

Proposed Exercises

- Exercise 1: Change the value of the presacler so that the rotation is faster, and the initial value of the register, so that another sequence comes out.

- Exercise 2: Use an 8-bit shift register, connecting the least signifcant 4 bits to the LEDs. This allows for making sequences in which all LEDs are off.

Conclusion

TODO